Wednesday, July 18, 2018 12:22 AM

## CS61C Discussion 9

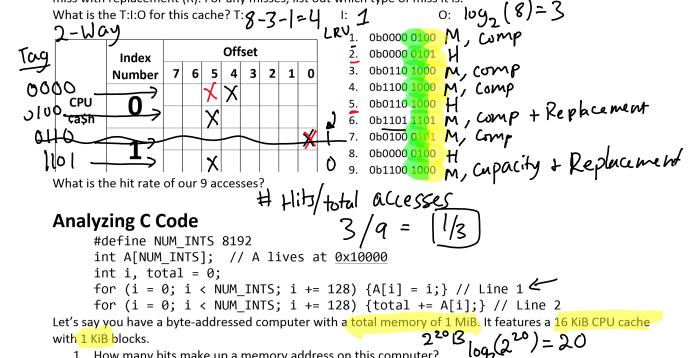

## **N-Way Set Associative**

Here's some practice involving a 2-way set associative cache, similar to last discussion's problem, except we have an 8-bit address space, classify each of the following accesses as a cache hit (H), cache miss (M), or cache miss with replacement (R). For any misses, list out which type of miss it is.

1. How many bits make up a memory address on this computer?

2. What is the T:I:O breakdown? Tag bits:

Offset bits: 10

3. Calculate the cache hit rate for the line marked Line 1:  $128 \cdot 4 = 27 \cdot 2^2 = 29$  Real : 2 50%

4. Calculate the cache hit rate for the line marked Line 2:  $192 \cdot 4 = 215$

16kiB = 16=24

**Average Memory Access Time**

AMAT is the average (expected) time it takes for memory access. It can be calculated using this formula:

$AMAT = hit time + miss rate \times miss penalty$

Miss rates can be given in terms of either local miss rates or global miss rates. The local miss rate of a cache is the percentage of accesses into the particular cache that miss at the cache, while the global miss rate is the percentage of all

GMR: % of all accesses that miss here - casculing Exercises LMR: % of accesses that miss

Suppose your system consists of:

- A L1\$ that hits in 2 cycles and has a local miss rate of 20%

- A L2\$ that hits in 15 cycles and has a global miss rate of 5%

- Main memory hits in 100 cycles

1. What is the local miss rate of L2\$?

$$25\% : 5\% = 20\% \cdot LMR$$

2. What is the AMAT of the system?

Tof.GMR = Tof. Access Rate. LMR

AMAT = 2 +20%·(15+25%·100) 1/111/27+0 3. Suppose we want to reduce the AMAT of the system to 8 or lower by adding in a L3\$. If the L3\$ has a local miss rate of 30%, what is the largest hit time that the L3\$ can have?

Now, what if we have a cache system with the following properties. What is the AMAT?

- L1\$ hits in 1 cycle (local miss rate 25%)

- L2\$ hits in 10 cycles (local miss rate 40%)

- L3\$ hits in 50 cycles (global miss rate 6%)

- Main memory hits in 100 cycles (always hits)

## Flynn Taxonomy

1. Explain SISD and give an example if available.

Single Instr Single Data

Explain SIMD and give an example if available.

Sing Inst Mult Data

Explain MISD and give an example if available.

Mult Inst Sing Data

Inst Mult Duta 4. Explain MIMD and give an example if available. MIMD 012 ... 7 First 4 bits offer 0/1  $\bigcirc$ 0