## Jon 112 Dis 6

Tuesday, October 2, 2018 11:05 AM

## CS 61C Fall 2018

## Caches II, Floating Point

Discussion 6: October 1, 2018

2Caches II, Floating Point

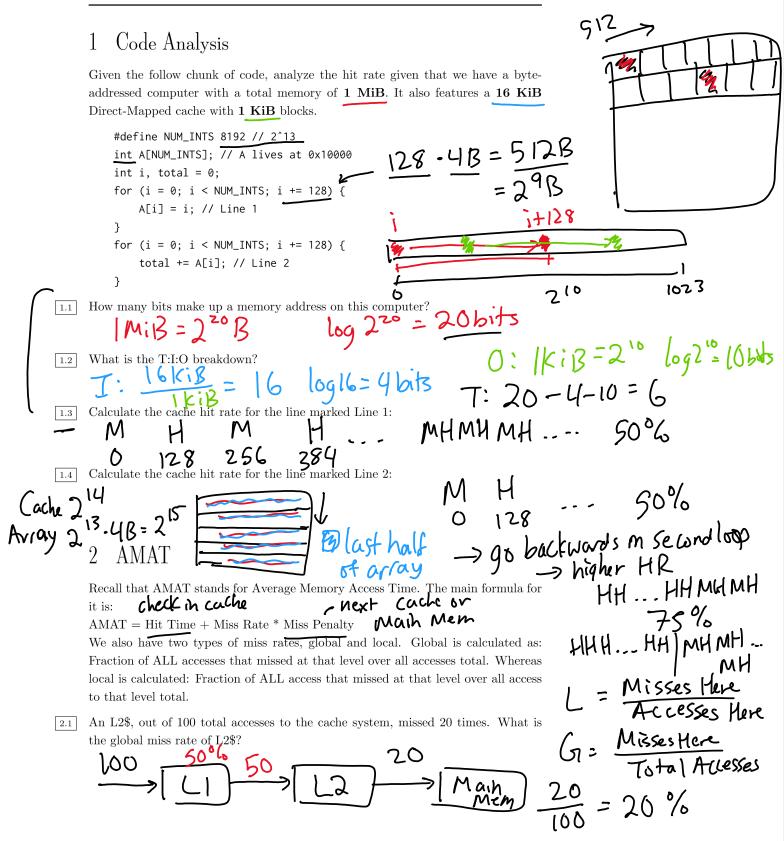

If L1\$ had a miss rate of 50%, what is the local miss rate of L2\$? 2.2

$$\frac{20}{50} = 40\%$$

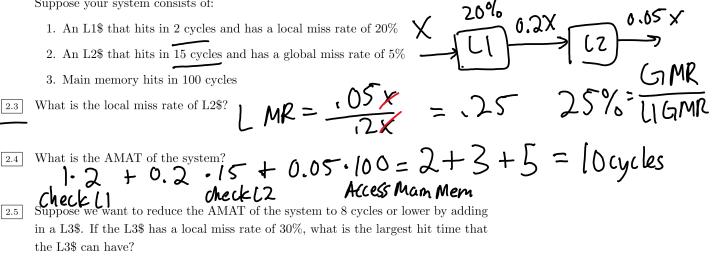

Suppose your system consists of:

## 3 Floating Point

The IEEE 754 standard defines a binary representation for floating point values using three fields:

- The sign determines the sign of the number (0 for positive, 1 for negative)

- The *exponent* is in **biased notation** with a bias of 127

- The significand or mantissa is akin to unsigned, but used to store a fraction instead of an integer

The below table shows the bit breakdown for the single precision (32-bit) represen-

( Kias: +127 1001b1 tation. 8 231 Mantissa/Significand/Fraction Sign Exponent For normalized floats: Value =  $(-1)^{Sign} * 2^{Exp-Bias} * 1.$ significand<sub>2</sub> For denormalized floats: Value =  $(-1)^{Sign} * 2^{Exp-Bias+1} * 0.$ significand<sub>2</sub> ()() -- O O's for Mantisa Meaning Exponent Significand expo Denorm 0 Anything ехрь 111\_\_\_\_]=+/- to ехро (11.\_\_\_]= NaN 1 - 254Normal Anything 255Infinity 0 255Nonzero NaN How many zeroes can be represented using a float? 3.1 0 0 - - - 0 0 HU - ()

254 - 127 = 127X Caches II, Floating Point 3 What is the largest finite positive value that can be stored using a single precision 3.2 0 1111 ... 1 => NaN float? \_23 7 FFFFF ÛХ What is the smallest positive value that can be stored using a single precision float? 3.3 What is the smallest positive normalized value that can be stored using a single 3.4precision float? Cover the following numbers from binary to decimal or from decimal to binary: 3.5 |.0000|.2exp: 3+127=130mankssa 0000100...0 Sign 0 1000. 1 • 0x00000000 • 39.5625 • 0xFF94BEEF • 8.25 • 0x00000F00 • -∞ Extra Stuff on Caches! 4 Heres some practice involving a 2-way set associative cache. This time we have 4.1 an 8-bit address space, 8 B blocks, and a cache size of 32 B. Classify each of the following accesses as a cache hit (H), cache miss (M) or cache miss with replacement (R). For any misses, list out which type of miss it is.

| Address     | T/I/O | Hit, Miss, Replace |

|-------------|-------|--------------------|

| 0b0000 0100 |       |                    |

| 0b0000 0101 |       |                    |

| 0b0110 1000 |       |                    |

| 0b1100 1000 |       |                    |

| 0b0110 1000 |       |                    |

| 0b1101 1101 |       |                    |

| 0b0100 0101 |       |                    |

| 0b0000 0100 |       |                    |

| 0b1100 1000 |       |                    |

[4.2] What is the hit rate of our above accesses?