## Jon 112 Dis 3

Tuesday, September 11, 2018 11:06 AM

CS 61C Fall 2018

**RISC-V** Intro Discussion 3: September 10, 2018

#### RISC-V: A Rundown 1

RISC-V is an assembly language, which is comprised of simple instructions that each do a single task such as addition or storing a chunk of data to memory.

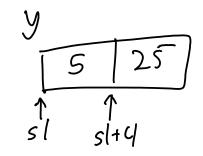

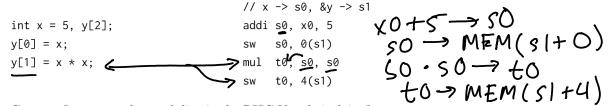

For example, on the left is a line of C code and on the right is a chunk of RISC-V code that accomplishes the same thing.

stach

Can you figure out what each line in the RISC-V code is doing? 1.1

#### 2 Registers

In RISC-V, we have two methods of storing data, one of them is main memory, the other is through registers. Registers are much faster than using main memory, but are very limited in space (32-bits)

|   | $\operatorname{Register}(s)$                                                                                                                                                                                                                      | Alt.             | Description                                                       |              |        |  |  |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------|--------------|--------|--|--|--|

| Π | x0                                                                                                                                                                                                                                                | zero             | The zero register, always zero                                    |              |        |  |  |  |

| T | x1                                                                                                                                                                                                                                                | ra               | The return address register, stores where functions should return |              |        |  |  |  |

|   | x2                                                                                                                                                                                                                                                | $^{\mathrm{sp}}$ | The stack pointer, where the stack ends                           | foo ( int a  | , ntb) |  |  |  |

|   | x5-x7, x28-x31                                                                                                                                                                                                                                    | t0-t6            | The temporary registers                                           |              | / /    |  |  |  |

|   | x8-x9, x18-x27                                                                                                                                                                                                                                    | s0-s11           | The saved registers                                               |              |        |  |  |  |

|   | x10-x17                                                                                                                                                                                                                                           | a0-a7            | The argument registers, a0-a1 are also return value               |              |        |  |  |  |

|   | Can you convert each instruction's registers to the other form?<br>add s0, zero, a1 $\rightarrow$ add $X $ , $f_{00} $ (a, b)<br>or x18, x1, x30 $\rightarrow$ or s2, va, t5<br>3 Basic Instructions<br>x = 2; |                  |                                                                   |              |        |  |  |  |

|   |                                                                                                                                                                                                                                                   | , here are       | e a couple of the basic instructions for arithmetic opera-        | 2→a0<br>6→a1 |        |  |  |  |

2.1

--> add X8, x0, x11 --> or s2, va, t5 add s0, zero, a1 or x18, x1, x30

#### 3 Basic Instructions

### 2 RISC-V Intro

**Basic Operations:**

| Adds the two argument registers and stores in destination register           |  |  |  |  |

|------------------------------------------------------------------------------|--|--|--|--|

| Exclusive or's the two argument registers and stores in destination register |  |  |  |  |

| ster                                                                         |  |  |  |  |

| Logical left shifts AR1 by AR2 and stores in DR                              |  |  |  |  |

| Logical right shifts AR1 by AR2 and stores in DR                             |  |  |  |  |

| Arithmetic right shifts AR1 by AR2 and stores in DR                          |  |  |  |  |

| parison                                                                      |  |  |  |  |

|                                                                              |  |  |  |  |

| у                                                                            |  |  |  |  |

| ister                                                                        |  |  |  |  |

|                                                                              |  |  |  |  |

|                                                                              |  |  |  |  |

|                                                                              |  |  |  |  |

|                                                                              |  |  |  |  |

| el                                                                           |  |  |  |  |

|                                                                              |  |  |  |  |

You may also see that there is an "i" at the end of certain instructions, such as addi, slli, etc. This means that AR2 becomes an "immediate" or an integer instead of using a register.

- 3.1 Assume we have an array in memory that contains int\* arr = {1,2,3,4,5,6,0}. Let the values of arr be a multiple of 4 and stored in register s0. What do the snippets of RISC-V code do? Assume that all the instructions are run one after the other in the same context.

- $arr[3] \rightarrow t0$   $t0 \cdot 4 \rightarrow t1$   $s0 + t1 \rightarrow t2$   $MEM(+2+0) \rightarrow t3$  t1 = 4.t0 t2 = s0 + 4.t0 t2 = s0 + 4.t0  $t3 + 1 \rightarrow t3$   $T \circ 7$   $t3 \rightarrow MEM(+2+0)$ --> a) lw t0, 12(s0) 50+4 +8 b) slli t1, t0, 2 add t2, s0, t1 lw t3, 0(t2) ivaf t07 addi t3, t3, 1 t3, 0(t2) SW t0, 0(s0)  $\zeta = - arr[o]$ c) lw  $MEM(s0+0) \rightarrow t0$ xori t0, t0, addi t0, t0, 1 While only using the instructions (and their "i" forms) given above, how can we

ЧĽ

2

9

3

3.2 While only using the instructions (and their "i" forms) given above, how can we branch on the following conditions:

s0 > s1 s0 < s1s0 > 1slt to, so, sl bne to, zero, label slt tu, su, sl beg tu, zero, label

# 4 C to RISC-V

[4.1] Translate between the C and RISC-V verbatim

| С                                                                                                                      | RISC-V                                                                                                   |              |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------|

| <pre>// s0 -&gt; a, s1 -&gt; b // s2 -&gt; c, s3 -&gt; z int a = 4, b = 5, c = 6, z; z = a + b + c + 10;</pre>         |                                                                                                          | -            |

| <pre>// s0 -&gt; int * p = intArr;<br/>// s1 -&gt; a;<br/>*p = 0;<br/>int a = 2;<br/>p[1] = p[a] = a;<br/>0 11=0</pre> | SW XO, O(SO)<br>addi SI, XO, 2<br>SU SI, 4(SO)<br>slli to, SI, 2<br>add to, SO, to<br>SW SI, O(to)       | jal x0, exit |

| <pre>// s0 -&gt; a, s1 -&gt; b int a = 5, b = 10; if(a + a == b) {     a = 0; } else { </pre>                          | addi s0, x0,5<br>addi s1, x0,10<br>add t0, s0, s0<br>bne t0, s0, else<br>add a0, x0, x0-<br>yal x0, exit | beq          |

| b = a - 1;<br>}                                                                                                        | al x0, exit<br>else:<br>addi s1, s0, 0<br>addi s1, x0, 1<br>addi t0, x0, 30                              |              |

|                                                                                                                        | loop:<br>beq s0, t0, exit<br>add s1, s1, s1<br>addi s0, s0, 1<br>jal x0, loop<br>exit:                   |              |

| <pre>// s0 -&gt; n, s1 -&gt; sum // assume n &gt; 0 to start for(int sum = 0; n &gt; 0; n) {    sum += n; }</pre>      |                                                                                                          |              |